| No. |

Features |

Year |

Chip |

International Conf. |

| 43 |

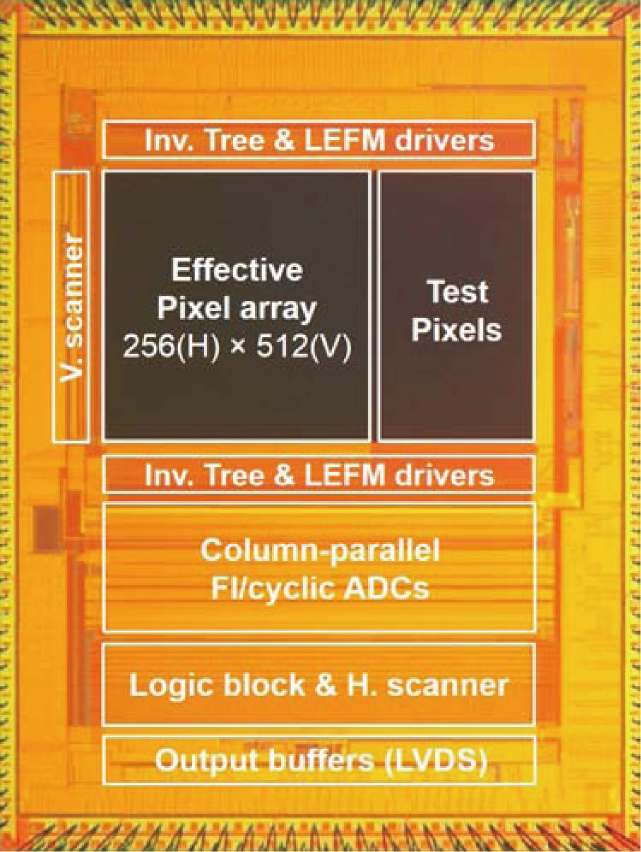

A 10.8ps-Time-Resolution 256x512 Image Sensor with 2-Tap True-CDS Lock-In Pixels for Fluorescence Lifetime Imaging |

2015 |

|

|

| 42 |

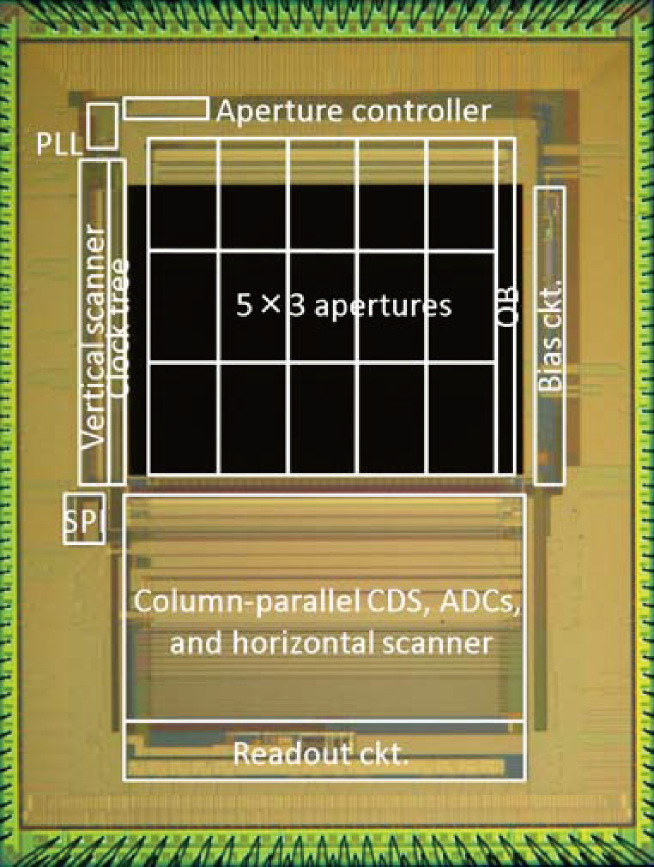

Single-Shot 200Mfps 5x3-Aperture Compressive CMOS Imager |

2015 |

|

|

| 41 |

A 0.3mm-Resolution Time-of-Flight CMOS Range Imager with Column-Gating Clock-Skew Calibration |

2014 |

|

|

| No. |

Features |

Year |

Chip |

International Conf. |

| 40 |

A 413x240-Pixel Sub-Centimeter Resolution Time-of-Flight CMOS Image Sensor with In-Pixel Background Canceling Using Lateral-Electric-Field Charge Modulators |

2014 |

|

|

| 39 |

A 33Mpixel 120fps CMOS Image Sensor Using 12b Column-Parallel Pipelined Cyclic ADCs |

2012 |

|

|

| 38 |

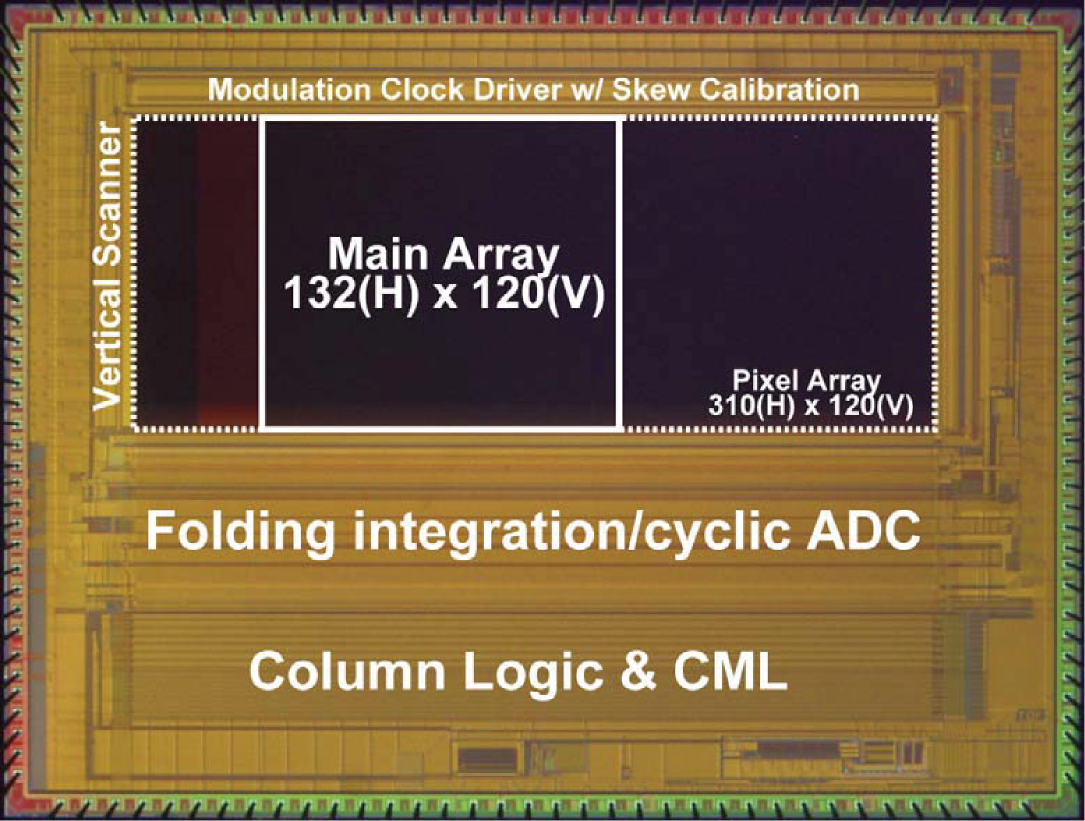

A Low-noise High-dynamic-range CMOS Imager with a 13-to-19b Variable-Resolution Column-Parallel Folding-Integration/Cyclic ADC

|

2011 |

|

|

| 37 |

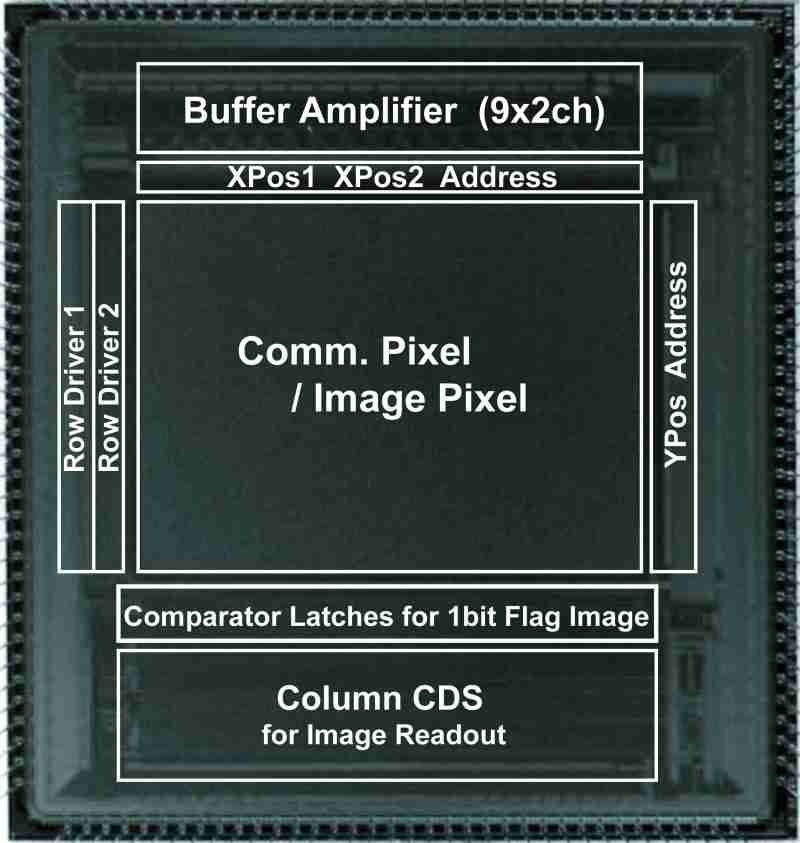

A CMOS Image Sensor for 10Mb/s 70m-Range LED-Based Spatial Optical Communication

|

2010 |

|

|

| 36 |

A 2.7e- Temporal Noise 99.7% Shutter Efficiency 92dB Dynamic Range CMOS Image Sensor with Dual Global Shutter Pixels

|

2010 |

|

|

| 35 |

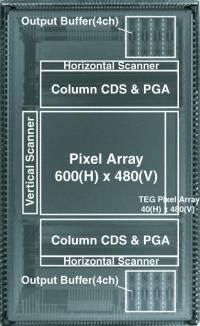

A CMOS imager and 2-D light pulse receiver array for spatial optical communication

|

2009 |

|

|

| 34 |

A low-noise wide-dynamic range high-frame rate CMOS image sensor using single-ended cyclic ADCs

|

2009 |

|

|

| 33 |

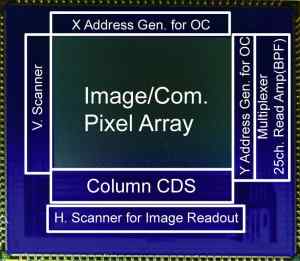

TOF Range Image Sensor Using A Range-Shift Technique

|

2008 |

|

|

| 32 |

A 15b 30MSample/s 123mW Pipeline A/D Converter with Linearized Settling Error Correction of Non-Slewing Closed-Loop Amplifiers

|

2008 |

|

|

| 31 |

The First 14bit Column-Parallel Cyclic A/D Converter and a CMOS Image Sensor Using Thereof. |

2008 |

|

|

| No. |

Features |

Year |

Chip |

International Conf. |

| 30 |

A High-Speed CMOS Image Sensor Integrating SIMD-type Column Parallel Image Compression Circuits |

2007 |

|

|

| 29 |

A 14b Low-power Pipeline A/D Converter Using a Pre-charging Technique

|

2007 |

|

|

| 28 |

A 1.0V 30mW 10b 100MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques (Figure of Merit (FOM) = 0.73 pJ/conv. The highest level in the world!!)

|

2006 |

|

|

| 27 |

A 3500fps High-speed CMOS Image Sensor with 12b Column-Parallel Cyclic A/D Converters |

2006 |

|

|

| 26 |

A CMOS TOF Range Image Sensor with Gates on Thick Oxide Structure

|

2005 |

|

|

| 25 |

A Cyclic A/D Converter with Pixel Noise and Column-wise Offset Canceling for CMOS Image Sensors

|

2005 |

|

|

| 24 |

A 160dB Wide Dynamic Range CMOS Image Sensor with Reduced-Offset 12-bit Column Parallel Cyclic ADCs |

2005 |

|

|

| 23 |

A 10b-per-rotation smart magnetic rotary encoder integrating an angle calculator

|

2005 |

|

|

22 |

A 120dB DR CMOS image sensor with a multiple exposure burst readout method and a 12b column parallel cyclic ADC

|

2005 |

|

|

| 21 |

A CMOS Magnetic Sensor Arrays Using Native-Substrate MAGFETs for a Smart Rotary Encoder

|

2004 |

|

|

| No. |

Features |

Year |

Chip |

International Conf. |

| 20 |

A wide DR CMOS image sensorusing multiple resolution column parallel ADC

|

2004 |

|

|

| 19 |

A CMOS rotary encoder using magnetic sensor arrays

|

2003 |

|

|

| 18 |

A high-speed low-power parallel pipeline A/D converter

|

2003 |

|

|

| 17 |

A high-sensitivity CMOS image sensor using an adaptive-gain column amplifiers

|

2003 |

|

|

| 16 |

A binocular CMOS image sensor for high-speed 3-D imaging |

2002 |

|

|

| 15 |

A high-speed (30MS/s) low-power(16mW) 10b ADC

|

2002 |

|

|

| 14 |

A high-speed image sensor for low-power motion-vector estimation

|

2000 |

|

|

| 13 |

wide-dynamic range CMOS image sensor with logarithmic response

|

1999 |

|

|

| 12 |

A high-sensitivity integrated digital fluxgate sensor

|

1999 |

|

|

| 11 |

A 2nd-order delta-sigma sensor interface for capacitive-type chemical sensors

|

1998 |

|

|

| No. |

Features |

Year |

Chip |

International Conf. |

| 10 |

A CMOS image sensor integrating low-power image compression circuits

|

1997 |

|

|

| 9 |

A delta-sigma interface chip for fluxgate magnetic sensors

|

1996 |

|

|

| 8 |

An integrated microfluxgate magnetic sensor

|

1996 |

|

|

| 7 |

A high-sensitivity microfluxgate magnetic sensor (Ver.2)

|

1995 |

|

|

| 6 |

A wave-parallel computing chip

|

1994 |

|

|

| 5 |

A two-dimensional silicon Hall element with micromaching

|

1993 |

|

|

| 4 |

A high-sensitivity microfluxgate magnetic sensor (Ver.1)

|

1993 |

|

|

3 |

A smart image sensor with current-mode parallel analog signal processing circuits

|

1991 |

|

|

| 2 |

A radix-2 Signed-Digit arithmetic IC chip using multiple-valued current-mode circuits

|

1989 |

|

|

| 1 |

The first multiplier LSI chip using multiple-valued current-mode circuits

|

1987 |

|

|