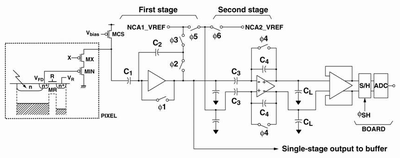

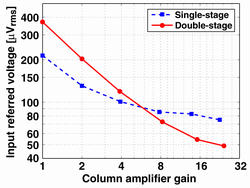

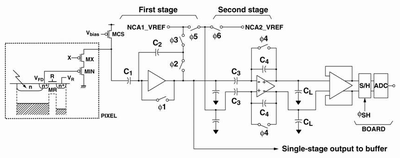

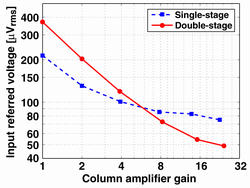

A very low-noise readout circuit can be realized with a high-gain column amplifier and a double-stage noise-canceling architecture which is composed two noise-canceling amplifiers for CMOS image sensors. As a result of the measurement of an implemented CMOS line image sensor, it is demonstrated that the proposed double-stage architecture showed the better noise performance than that of the single-stage for high-gain. 49.1uVrms can be obtained as the noise voltage.

|

|

| Implemented signal readout circuit for CMOS image sensors. | Noise reduction effect. |