カラム集積巡回型A/Dコンバータ

1段巡回型A/Dコンバータ

CMOSイメージセンサにおいて,A/D変換器をカラムに集積することによって、イメージセンサの

低ノイズ化、高速読みたし、低消費電力化と共に 動作速度の低減などが可能になります。

本研究室では多数の巡回型カラム並列A/D変換器の設計、試作、測定を行い、得られた結果に基づいた

カラムA/D変換器に関するノウハウの蓄積と共に性能向上を果たしてきました。

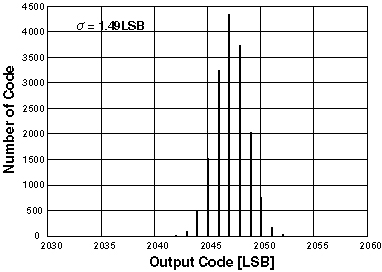

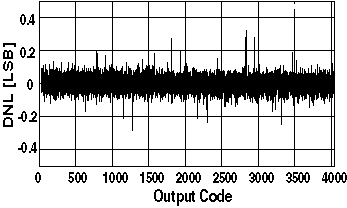

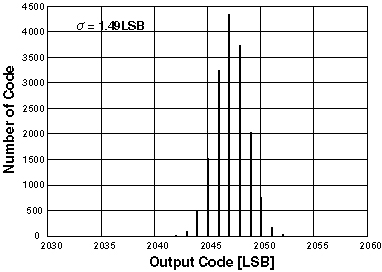

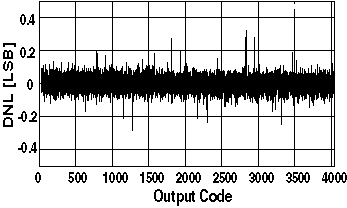

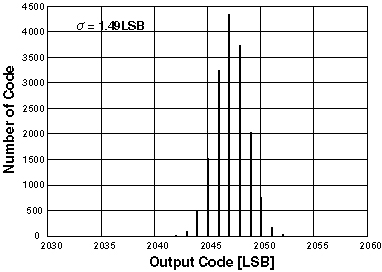

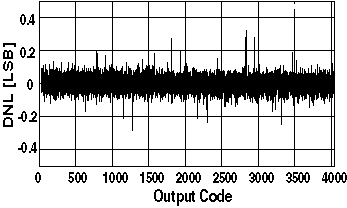

その成果の1つとして、12ビット、1V Full Scaleのカラム並列A/D変換器を測定した結果、ランダムノイズが

363 uVrms、微分非直線性(DNL)が0.3LSBの性能が得られました。

|

|

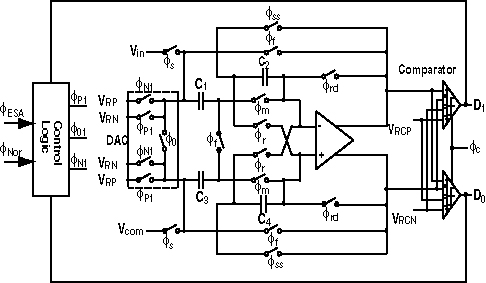

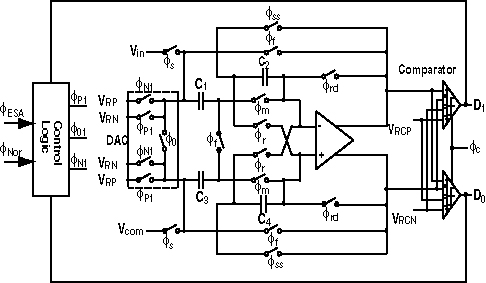

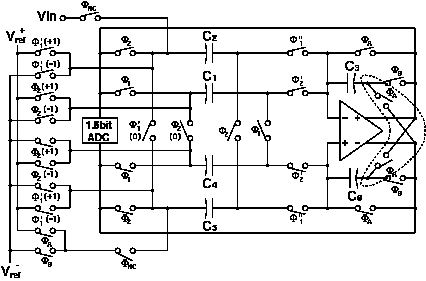

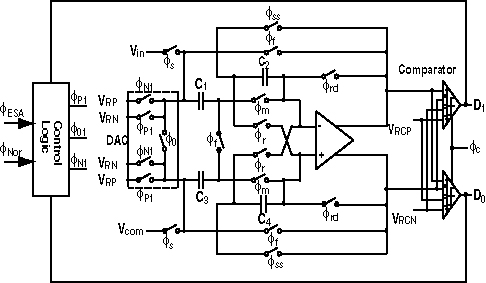

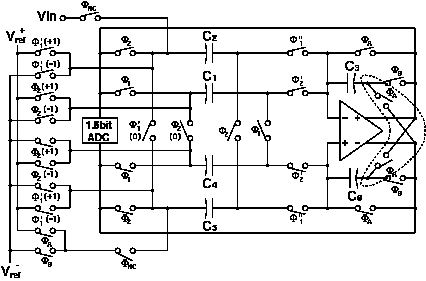

| ノイズ除去回路を含む12ビットカラム並列巡回型A/D変換器

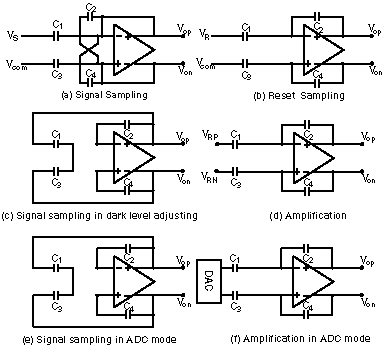

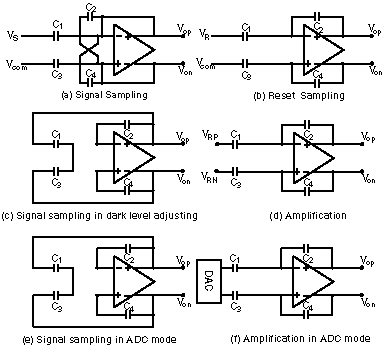

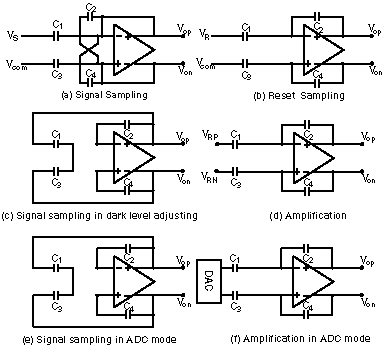

| 動作ペースことの回路接続

|

|

|

| A/D変換器のノイズヒストグラム

| A/D変換器の微分非直線性(DNL)

|

2段巡回型A/Dコンバータ

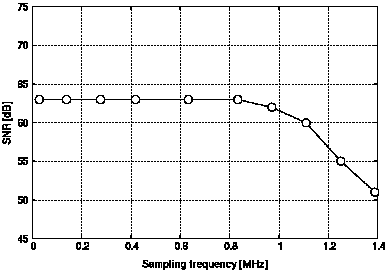

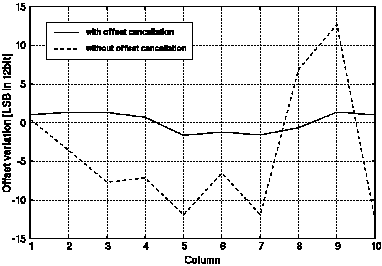

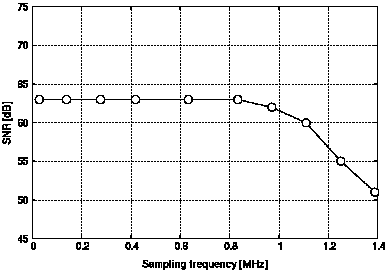

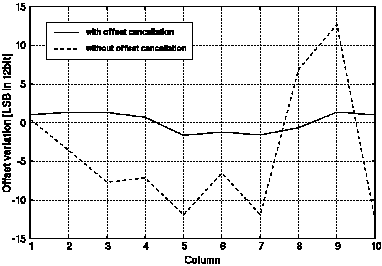

CMOSイメージセンサにおいて,アンプ共有巡回型A/D変換器のカラム集積は,画素信号の低ノイズ読み出しと,高速高分解能A/D変換器の低消費電力化が期待できる技術として注目されています.巡回型A/D変換器では,アンプ共有化のため,これまでカラム毎のアンプのオフセットばらつきがFPNの性能劣化要因となっていました.この問題に対し,アンプ出力にたすきがけ接続スイッチを設けたオフセットキャンセルアーキテクチャを提案し,設計,試作を行った結果,オフセットばらつきを12ビット分解能で12LSBp-pから1.5LSBp-pにまで低減できることに成功しました.また,カラムピッチ20um,消費電力0.43mWで64dB@1MspsのSNR性能が得られました.

|

|

| オフセットキャンセル機能を有するカラム巡回型A/D変換器

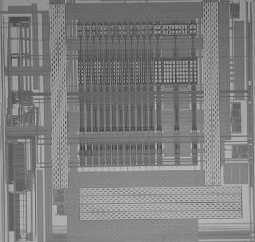

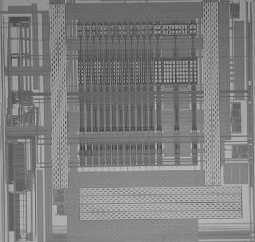

| 試作チップ写真

|

|

|

| SNRとサンプリング周波数との関係

| カラムオフセットばらつき低減効果

|

文献

- M. Mase, S. Kawahito, M. Sasaki, Y. Wakamori, and M. Furuta, "

A Wide Dynamic Range CMOS Image Sensor with Multiple Exposure-Time Signal Outputs and 12-bit Column-Parallel cyclic A/D Converters,"

IEEE Journal of Solid-State Circuits, vol. 40, No. 12, pp. 2787-2795, Dec., 2005

- J. H. Park, M. Mase, S. Kawahito, M. Sasaki,

Y. Wakamori, and Y. Ohta, " A 142dB Dynamic Range CMOS Image

Sensor with Multiple Exposure Time Signals,"," Proc. 2005 ASSCC

A2L-3, pp. 85-88, Taiwan, Nov. 2005.

- M. Furuta, S. Kawahito, T. Inoue, Y. Nishikawa,"A cycic A/D converter with pixel noise and column-wise offset cancellation for CMOS image sensors", Proc. European Solid-State Circuits Conf., pp.411-414, 2005

- M. Furuta, T. Inoue, Y. Nishikawa, and S. Kawahito, "

A 3500 fps High-Speed CMOS Image Sensor with 12b Column-Parallel Cyclic A/D Converters,"

Symp. VLSI Circuits Dig., pp. 27-28, Jun., 2006.

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: webmaster@idl.rie.shizuoka.ac.jp