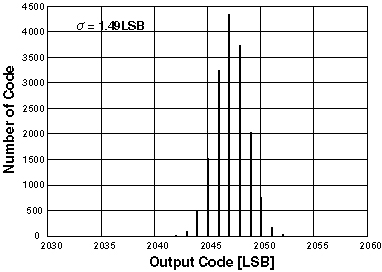

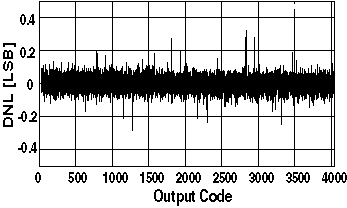

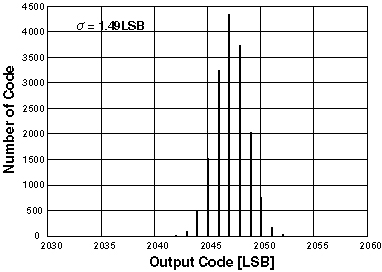

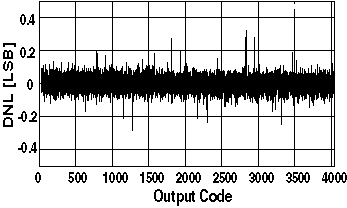

High performance CMOS image sensor with low noise, high-speed signal readout, low power consumption, and slow operation rate of ADC can be achived by implementing column parallel ADCs. We have been integrated know-how by design and testing ADCs several times, which leads to performance enhancements of column parallel cyclic ADCs. As a result, measured random noise is reduced to 1.49 LSB, which corresponds to 363 uVrms in 12-bit, 1 V full-scale, and the differential non-linearity (DNL) is within +0.3 LSB / -0.3 LSB.

|

|

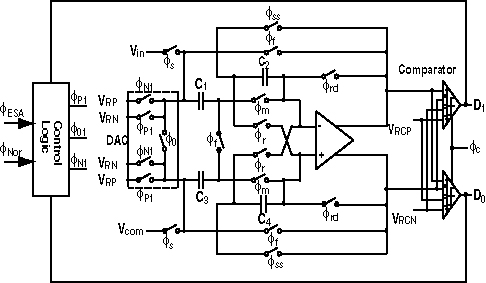

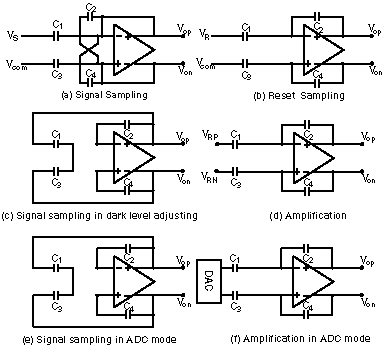

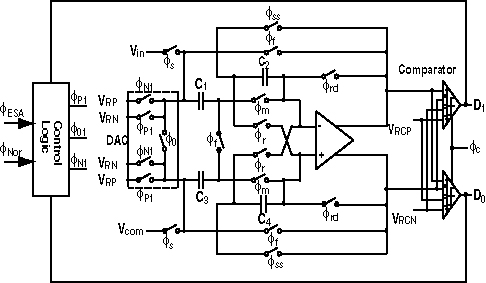

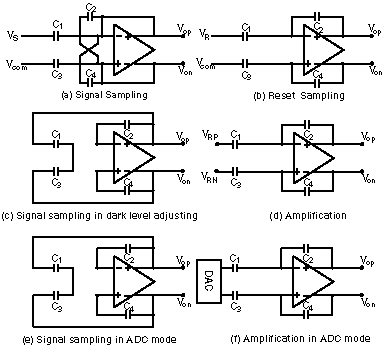

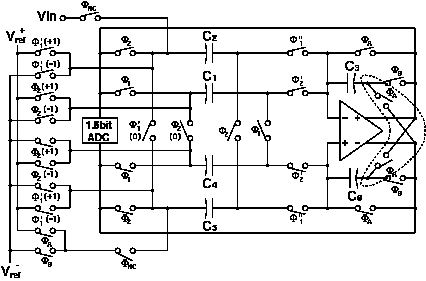

| 12-bit column parallel cyclic ADC with noise cancellation circuit. | Circuit connection for each working phase. |

|

|

| Histogram plot with DC input. | Differential non-linearity (DNL) plot. |

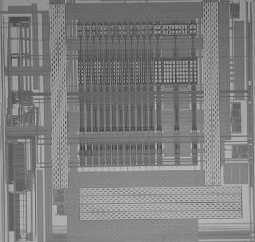

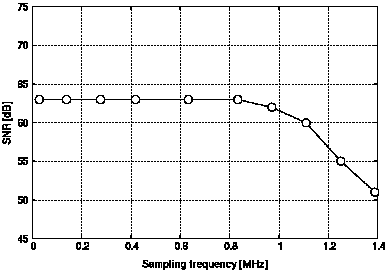

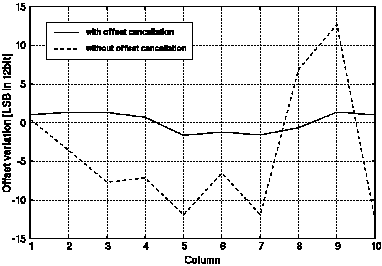

A cyclic ADC with pixel noise cancel and column-wise offset cancelling for CMOS image sensor is developed. By adding cross connected switches to a cyclic ADC, a column-wise fixed pattern noise due to the amplifier's offset variation is greatly reduced. A prototype 12-bit cyclic ADC implemented using 0.25um CMOS technology exhibits a 1.5mVp-p column-wise offset deviation. The ADC has 62dB SNR at 1Msample/s. The power dissipation is 0.43mW at 3.3V supplies, and the area of one channel is 0.04mm x 1.2mm.

|

|

| Schematic of the proposed cyclic ADC with the pixel and column-wise FPN canceling. | Chip photograph. |

|

|

| SNR vs sampling frequency. | Comparison of the offset variation. |